## **Logic Analysis Basics**

## February 11, 2003

presented by:

Sarah Herron

## Agenda

- Overview of a Logic Analyzer

- Logic Analyzer Process

- Connect (Probing)

- Acquire

- Timing Analyzer

- State Analyzer

- Data Analysis Tools and Display

- Conclusion

Page 3

Agilent Technologies

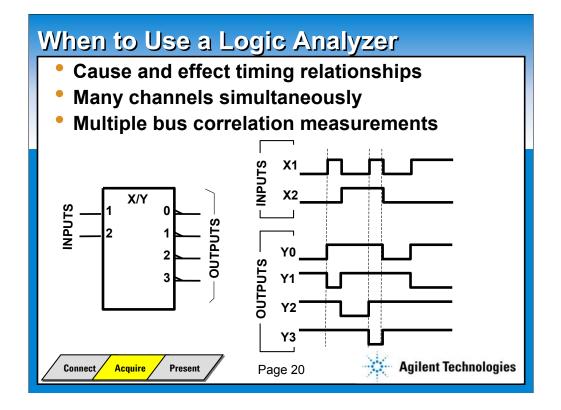

You should use a logic analyzer:

-When you need to see many signals at once.

-When you need to look at signals in your system the same way your hardware does.

-When you need to trigger on a pattern of highs and lows on several lines and see the results.

-When you need to monitor the behavior of complex systems including HW/SW integration

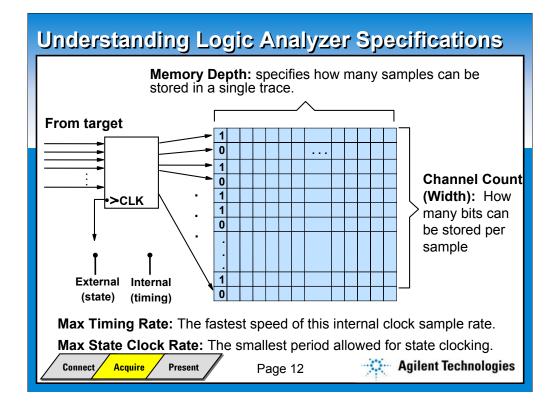

Logic Analysis has always been positioned for consideration in terms of the 'banner specifications' of Acquisition speed, memory depth, and channel count. Of course these are still very important. If it is not fast enough, deep enough, or wide enough to capture your data, there is no point considering it further.

But once you move beyond those specs, you must still consider the solution as a whole. Many of the 'details' can make or break your ability to debug your system.

Let's run through some critical factors for consideration....

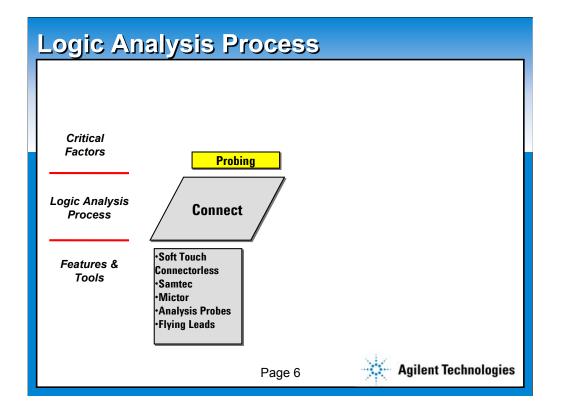

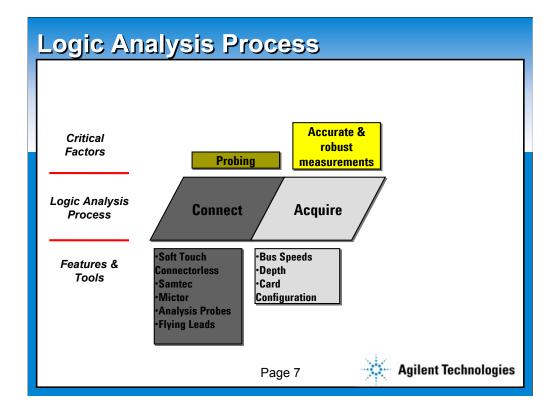

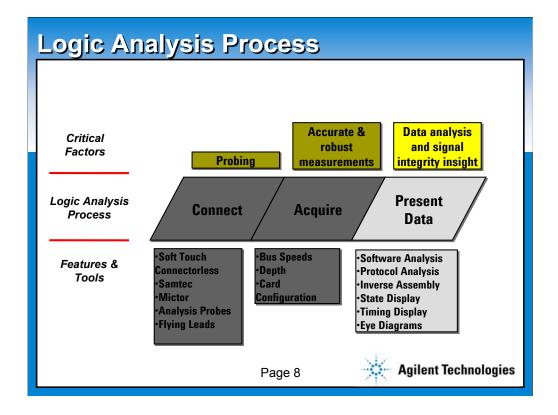

First, you have the probing problem and if you don't get this done right, the rest of the process is at risk. Probing comprises the Connection part of the process and Agilent offers a variety of solutions to meet your needs.

The second consideration is how you are going to make accurate and robust measurements. This is the Acquire part of the process and there are a variety of solutions to meet different needs.

Finally, you have to analyze the data, and insome cases, this requires additional insight into signal integrity. This is the Present data phase and there are a variety of ways to look at the acquired data.

CONNECT-ACQUIRE-PRESENT – If you think about your logic solution in terms of this model you can begin to see the big picture that goes beyond banner specs.

The rest of our slides will walk through each of these steps and show you some things that Agilent believes truly add unique value and when combined, offer an unparalleled solution.

Logic Analysis has always been positioned for consideration in terms of the 'banner specifications' of Acquisition speed, memory depth, and channel count. Of course these are still very important. If it is not fast enough, deep enough, or wide enough to capture your data, there is no point considering it further.

But once you move beyond those specs, you must still consider the solution as a whole. Many of the 'details' can make or break your ability to debug your system.

Let's run through some critical factors for consideration....

First, you have the probing problem and if you don't get this done right, the rest of the process is at risk. Probing comprises the Connection part of the process and Agilent offers a variety of solutions to meet your needs.

The second consideration is how you are going to make accurate and robust measurements. This is the Acquire part of the process and there are a variety of solutions to meet different needs.

Finally, you have to analyze the data, and insome cases, this requires additional insight into signal integrity. This is the Present data phase and there are a variety of ways to look at the acquired data.

CONNECT-ACQUIRE-PRESENT – If you think about your logic solution in terms of this model you can begin to see the big picture that goes beyond banner specs.

The rest of our slides will walk through each of these steps and show you some things that Agilent believes truly add unique value and when combined, offer an unparalleled solution.

Logic Analysis has always been positioned for consideration in terms of the 'banner specifications' of Acquisition speed, memory depth, and channel count. Of course these are still very important. If it is not fast enough, deep enough, or wide enough to capture your data, there is no point considering it further.

But once you move beyond those specs, you must still consider the solution as a whole. Many of the 'details' can make or break your ability to debug your system.

Let's run through some critical factors for consideration....

First, you have the probing problem and if you don't get this done right, the rest of the process is at risk. Probing comprises the Connection part of the process and Agilent offers a variety of solutions to meet your needs.

The second consideration is how you are going to make accurate and robust measurements. This is the Acquire part of the process and there are a variety of solutions to meet different needs.

Finally, you have to analyze the data, and insome cases, this requires additional insight into signal integrity. This is the Present data phase and there are a variety of ways to look at the acquired data.

CONNECT-ACQUIRE-PRESENT – If you think about your logic solution in terms of this model you can begin to see the big picture that goes beyond banner specs.

The rest of our slides will walk through each of these steps and show you some things that Agilent believes truly add unique value and when combined, offer an unparalleled solution.

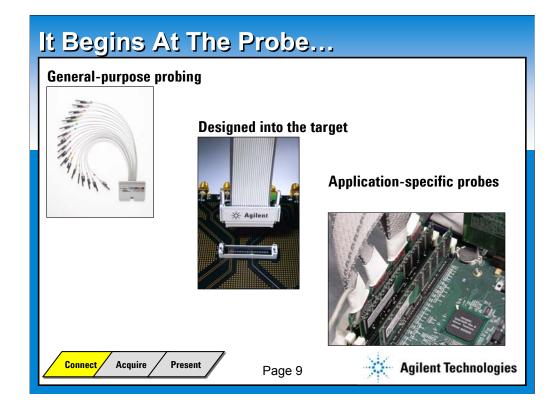

Let's start with the connection phase...

You must get probing right if want to make dependable measurements. It starts there and it can be the limiting factor in your ability to acquire data if it is not done properly. Probing is not an easy decision because it is often about the tradeoffs that must be made around its electrical and mechanical impact on your system. You can not escape the fact that probing is invasive but you can minimize how invasive it is.

What kind of probe you need depends on what you're making measurements on. In many cases you need to attach probes to buses or signals directly on your PC board. in other cases, Agilent and our premier solution partners provide what we call analysis probes, which are tailored to the needs of a specific interconnect standard. The one shown on the right is a DDR memory probe

Today we will concentrate on the first two - particularly the recent innovations in connectorless probing for general purpose applications.

Lets first take a step back and think about probing in a more general sense. We believe that there are some very well defined factors that define a good probing solution and we have listed them here. I imagine if you were to define your perfect probe it would hit on all or most of these things.

In the past, we have always viewed the first 2 categories as 'musts' when it came to probe design. Of course there are always tradeoffs and a certain threshold of what is acceptable. There is no perfect probe.

The last category has always been the icing on the cake but users have been willing to compromise on these if it gets them to their data.

So why bring this up?

As probing technology advances, you hope to continually decrease the size and number of tradeoffs. Advancing technology demands this.

The latest innovations in gp probing revolve around the concept of 'Connectorless Probing' and this innovation is currently receiving a lot of attention as the superior approach to gp probing. Both Tek and Agilent are offering a connectorless solution but are using VERY different approaches. The old way, and the way Tek is currently doing it, is an elastomeric compression probe. Agilent's solution is what we consider to be a generation beyond elastomeric probing. We also believe it moves beyond some of the old tradeoffs you had to put up with.

Lets look at a little history around connectorless solutions.....

Lets first take a step back and think about probing in a more general sense. We believe that there are some very well defined factors that define a good probing solution and we have listed them here. I imagine if you were to define your perfect probe it would hit on all or most of these things.

In the past, we have always viewed the first 2 categories as 'musts' when it came to probe design. Of course there are always tradeoffs and a certain threshold of what is acceptable. There is no perfect probe.

The last category has always been the icing on the cake but users have been willing to compromise on these if it gets them to their data.

So why bring this up?

As probing technology advances, you hope to continually decrease the size and number of tradeoffs. Advancing technology demands this.

The latest innovations in gp probing revolve around the concept of 'Connectorless Probing' and this innovation is currently receiving a lot of attention as the superior approach to gp probing. Both Tek and Agilent are offering a connectorless solution but are using VERY different approaches. The old way, and the way Tek is currently doing it, is an elastomeric compression probe. Agilent's solution is what we consider to be a generation beyond elastomeric probing. We also believe it moves beyond some of the old tradeoffs you had to put up with.

Lets look at a little history around connectorless solutions.....

The shaded area shown above represents the total, finite amount of logic analyzer memory. This memory may be distributed in various ways. When the analyzer is used in Full Channel mode, there is a maximum of 128M memory on each channel.

The memory may be reduced at any time to speed up traces of infrequent events, if desired. Individual channel memory may also be doubled by switching to Half Channel mode (Timing mode only).

This redistributes the same amount of memory over half as many channels, doubling the number of samples/window of time that may be stored on remaining channels.

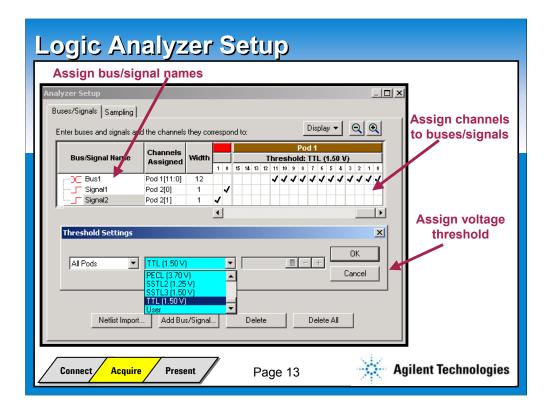

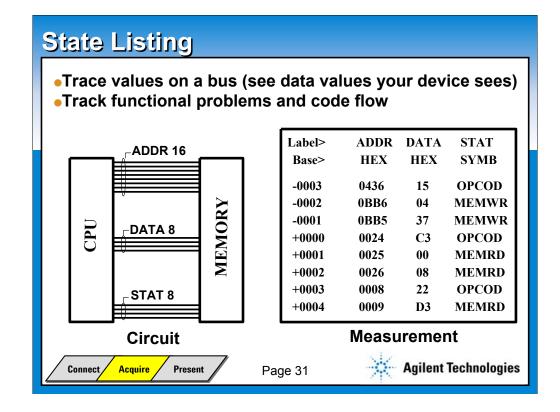

State measurements must be displayed in a format easy for the user to interpret and analyze. The logic analyzer can be programmed through a configuration menu to [highlight 1] group the measurement channel results under descriptive labels like [highlight 2] ADDR, DATA and STAT. These labels identify the measured states for the address, data and control busses, respectively. This configuration [show 3] is called the state format specification.

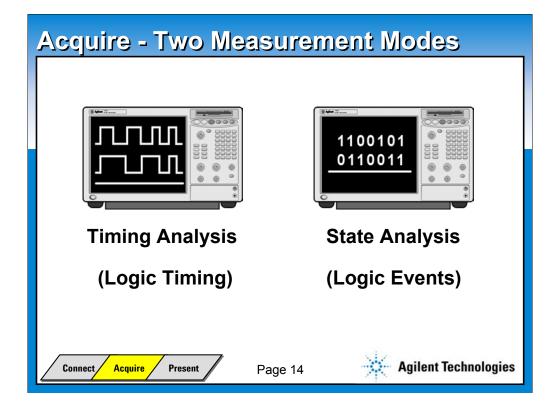

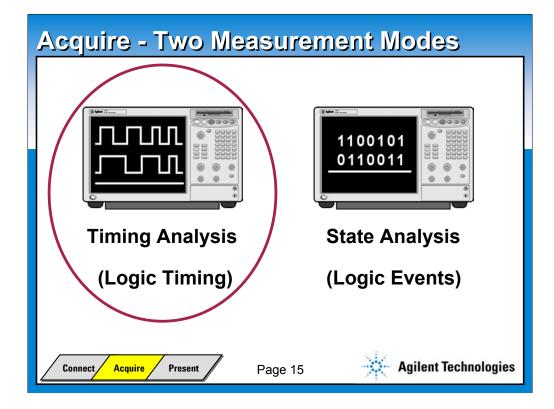

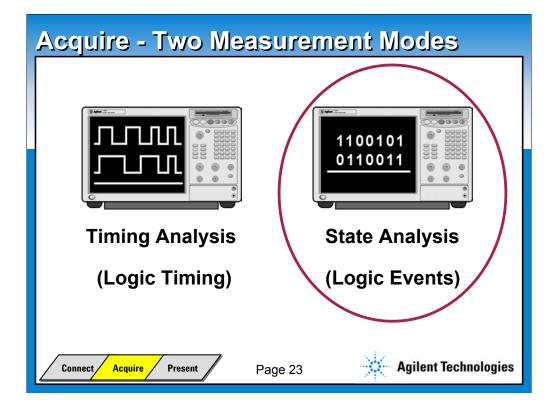

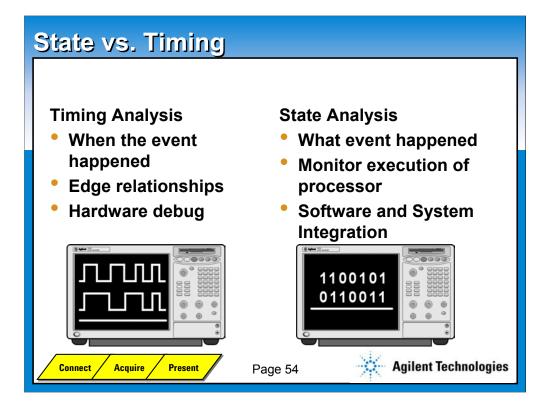

Two types of measurements are performed in logic analysis: state and timing measurements. A logic analyzer contains both a state analyzer and a timing analyzer.

The state analyzer measures the occurrence of logic states or events and represents them as numbers.

The timing analyzer measures the timing of logic states or events and represents that information as waveforms.

Let's begin with a discussion of Timing Analysis

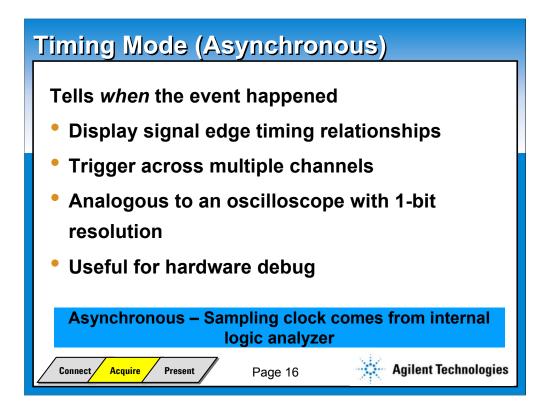

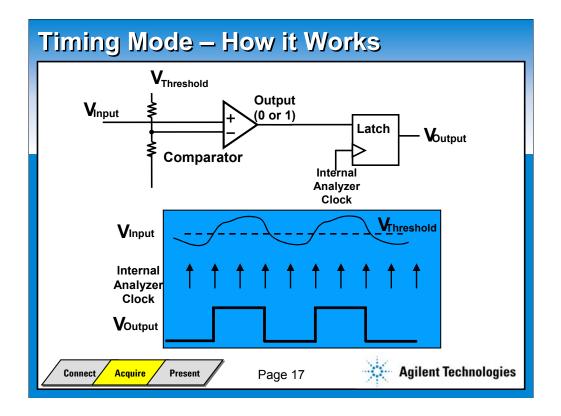

A timing analyzer is the part of a logic analyzer that is like a digitizing scope with one bit of vertical resolution and many channels. It displays information in the same general form as a scope, with the horizontal axis representing time and the vertical axis as voltage amplitude.

With one bit of resolution, you can display only two states – high or low. It samples data at regular time intervals using an internal clock.

This data is usually displayed in a waveform view similar to an oscilloscope. 0 represents below threshold and 1 represents above threshold. Because the waveform is time-dependent, the waveform display is said to be in the "time domain".

The output in timing mode is a square wave representing the value with respect to threshold of the signal at the time it was sampled (at each internal clock edge).

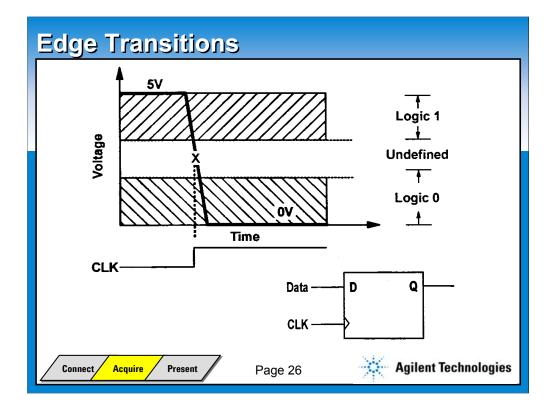

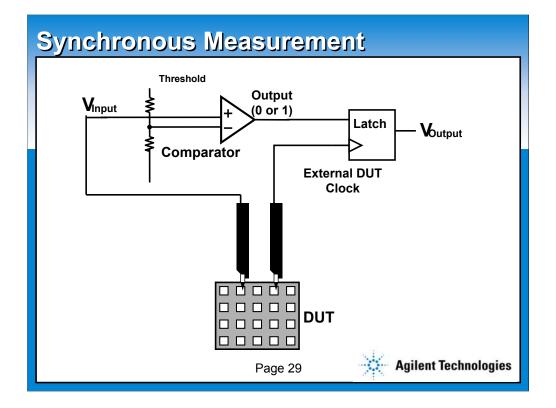

The comparator output provides a signal with stable voltage levels to the measurement channel. To digitize this signal a timing reference, or clock signal, is needed. The measurement channel uses a latch, and a clock signal from either the DUT or the logic analyzer to convert the comparator output to digital data.

| Timing W        | /aveform        |           |              |            |

|-----------------|-----------------|-----------|--------------|------------|

| Scale 5 ns/div  |                 | Delay Os  |              |            |

| Bus/Signal      | 15 ns -10 ns    | -5 ns 0 s | 5 ns 10 ns   | 15 n       |

| Sample Number   | -6              |           |              | 6 <b>-</b> |

| ⊞Bus1           | XFAXFBXFCXFC    |           | 01 02 03 04  | 05         |

| Signal1         |                 | 1 0 1     | 0 1 0 1      | 0 1        |

| Signal2         | 1 0             | 1 0       | 1 0          | 1          |

| Time            | -15 ns<br>I I I |           |              | 15 ns<br>I |

|                 |                 |           |              | -          |

|                 |                 |           |              |            |

| Connect Acquire | Present         | Page 18   | Agilent Tech | nologies   |

Each sample clock active edge, tells the analyzer when to acquire a sample. In timing mode, the sample clock comes from the logic analyzer module. In state mode, the sample clock is derived from the device under test, usually a bus clock.

The timing analyzer oversamples the signal much like an oscilloscope so that the device activity between states can be seen.

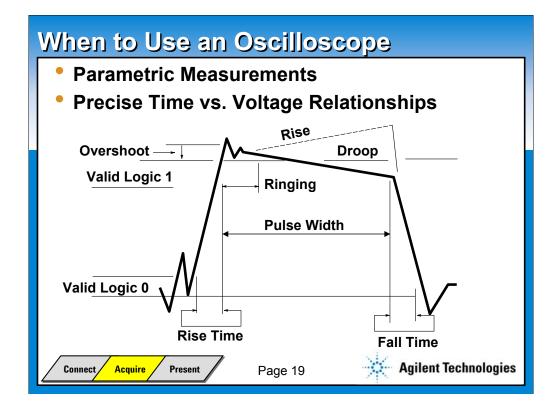

Since a logic analyzer only has one comparator per channel, it cannot faithfully reproduce a signal, it can only determine whether the signal at the time of sampling is above or below the threshold voltage. In order to take parametric measurements and accurately view signal characteristics, an oscilloscope must be used.

Timing analysis sacrifices the resolution of an oscilloscope in order to gain access to many channels simultaneously. The ability to monitor signals on all of the busses at any given time provides a clear picture of what is going on inside the microprocessor.

While scopes are usually limited to 4 channels, logic analyzers can probe, acquire and display 100s of channels simultaneously.

Conventional mode is most effective for signals which transition frequently and/or which occur over a brief period of time.

With this mode, however, there is a trade-off between resolution and total acquisition time. Remember that every sampling point uses one memory location. Thus, the higher the resolution (faster sampling rate), the shorter the acquisition window.

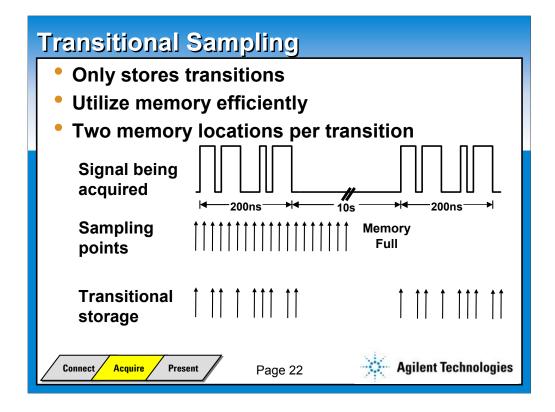

Transitional sampling, makes more efficient use of memory by storing only those samples that were preceded by a transition, together with the elapsed time from the last transition. Thus we use only two memory location per transition and no memory at all if there is no change in activity.

In this example, we are sampling at 200MHz, or in 5ns increments. It would take 40 memory locations to store the initial burst of information. It would then take an additional 2 million memory locations to store the 10s of deadtime. Instead of wasting all of these locations, Transitional timing will only capture when there is a transition. This means only 2 storage positions are required for the entire 10s of deadtime.

Now let's switch gears and talk about State Analysis

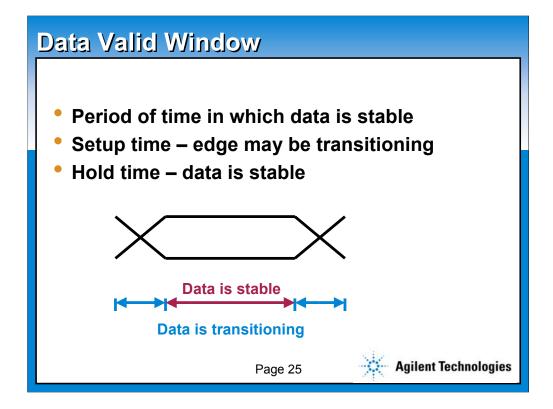

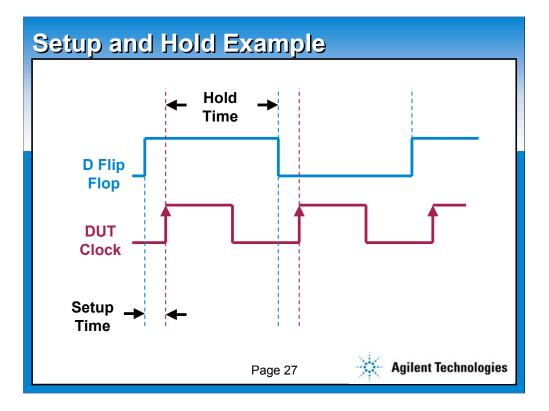

Setup time and hold time are important characteristics of digital devices. They are defined by the semiconductor manufacturer of the particular device.

For the D flip-flop to operate correctly, the D input must be stable at a valid logic level for a specific time before the rising clock edge. This time is called the setup time .

There may also be a requirement that the D input remain stable for short time after the clock edge. This time is called the hold time.

Why is setup and hold time important? Imagine what would happen if the clock edge occurred at the same time the data was switching through the undefined zone without the data being held stable for a fixed period.

In the example above, 5 V is high and 0 V is low. The voltage at the clock edge is in the undefined zone of voltages. At this voltages it is impossible to determine whether a logic 1 or a logic 0 is clocked into the flip-flop. It may be either.

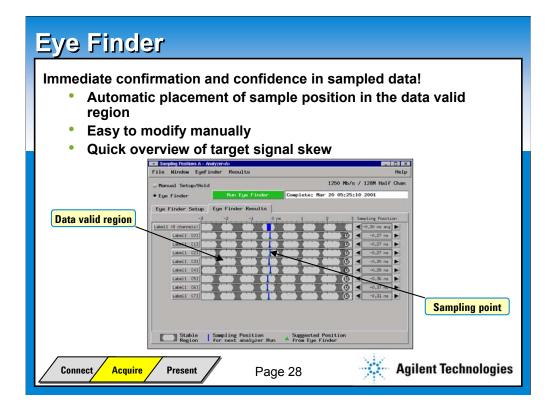

Agilent takes the commitment to reliable measurements seriously. Agilent chose a simple, reliable sampling architecture for logic analyzers, and we provide you an indispensable aid for reliable state measurements: eye finder. Without going into too deep technical detail, the challenge is to find the center of the data valid eye for each signal coming into the logic analyzer; to set the sampling point to the center of the eye on each channel; and to make sure it stays there.

Eye finder examines the signals in your circuit for millions of clock cycles to find the data valid regions. In the eye finder display, the data valid regions are the clear regions. The sampling points selected by eye finder are indicated in blue.

The center of the screen (0 ns) corresponds to the clock.

Independent of the sample position setting, Eye Finder also provides a very fast view of target signal skew. If a particular signal in a bus is skewed out of alignment with the rest of the bus, eye finder will show it. With older analyzers, this sort of problem would be effecting your data significantly and could be extremely difficult to find.

In a synchronous measurement, a synchronizing signal is taken from the DUT and used by the measurement channel as a timing, or clock signal. The clock signal provides the timing information required to identify valid logic states of the DUT and convert them to data.

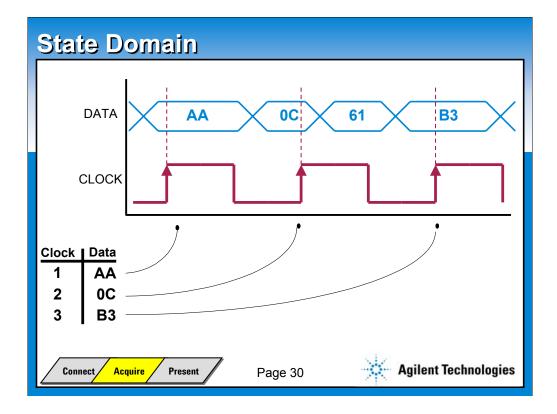

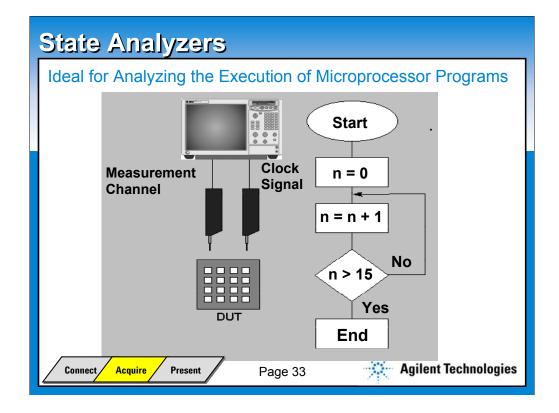

A state analyzer samples data based on an external clock . Each time the state analyzer receives a qualified edge from the device under test (DUT), it samples and stores each input in the trace buffer. Data collected in this manner is typically displayed as a sequential list of logical states in a listing display.

State analysis uses the clock on the device under test as the sampling clock. This means that data is only sampled when it is valid. The output in state mode is a listing of the values that crossed the bus, with the option of a time stamp noting when the values occurred.

|             | umber      | ADDR                   | DATA                   | STAT               | MPC821/860 PowerQUICC Inverse As |  |

|-------------|------------|------------------------|------------------------|--------------------|----------------------------------|--|

|             | =          | - FFF0 386B            | =                      | =                  |                                  |  |

|             | -24        | 1110 3037              | DUHL USEY              | UD USE7            | 102 13,0X4100(112)               |  |

|             | -23<br>-22 | 0000 41B0<br>0000 41B1 | 0041 23D7              | 03 23D7            | mem read 0x00                    |  |

|             | -22        | 0000 4181              | 0041 23D7<br>EF41 23D7 | OB 23D7<br>13 23D7 | mem read OxOO<br>mem read Oxef   |  |

|             | -21        | 0000 4182              | 7241 23D7              | 0B 23D7            | mem read 0x22                    |  |

|             | -16        | FFF0 385B              | 7041 03E7              | OB 03E7            | srawi r8,r5,d31                  |  |

|             | -12        | FFF0 385F              | FF41 03E7              | 0B 03E7            | andi. r7,r8,0x03ff               |  |

|             | -8         | FFF0 3863              | 1441 O3E7              | 0B 03E7            | add r11,r7,r5                    |  |

|             | -4         | FFF0 3867              | 0041 03E7              | 0B 03E7            | addi r9,r0,0xfc00                |  |

| ∎⊢          | 0          | FFFO 386B              | 3841 03E7              | OB 03E7            | and r10,r11,r9                   |  |

| <b>_</b>    | 4          | FFFO 386F              | 5041 03E7              | OB 03E7            | subf r8,r10,r5                   |  |

|             | 8          | FFF0 3873              | 0041 03E7              | OB 03E7            | addis r12,r0,0x0000              |  |

| <u>M2</u> + | 12         | FFF0 3877              | 4941 03E7              | OB 03E7            | lbz r11,0x4349(r12)              |  |

|             | 13         | 0000 4349              | 0141 23D7              | OB 23D7            | mem read 0x01                    |  |

|             | 17         | FFF0 387B              | 7441 O3E7              | OB 03E7            | extsb r11,r11                    |  |

|             | 21         | FFF0 387F              | D641 03E7              | OB 03E7            | divw r7,r8,r11                   |  |

|             | 25         | FFFO 3883              | 0041 03E7              | OB 03E7            | emp cr0,0,r6,r7                  |  |

|             | 29         | FFF0 3887              | C441 03E7              | OB 03E7            | bc d12,d0,0xfff0384              |  |

|             | 33         | FFF0 384B              | 0141 03E7              | OB 03F7            | addi r6 r6 OvOOO1                |  |

The logic analyzer can go even further with inverse-assembler capability, and display the actual assembly language code executed by the system. This allows the user to easily check the program code executed by the microprocessor.

State measurements are useful for monitoring and analyzing the execution of computer software programs. State analyzers are excellent tools to debug and optimize computer code.

State analyzers have sequence levels that aid triggering and storage. Sequence levels allow you to qualify data storage more accurately than a single trigger point. This means that you can more accurately window in on the data without storing information you do not need.

Sequence levels usually look something like this: 1 find XXXX else on XXXX go to level x 2 then find XXXX else on XXXX go to level X 3 trigger on XXXX

Sequence levels are especially useful for getting into a subroutine from a specific point in the program.

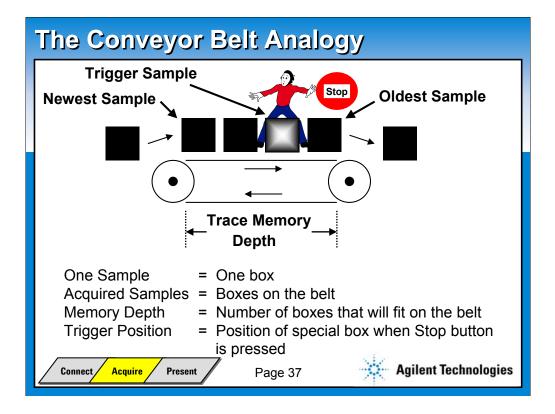

The memory of a logic analyzer can be compared to a very long conveyor Belt, and the samples acquired from the Device Under Test (DUT) as boxes on the Conveyor Belt. At one end, new boxes are placed on the conveyor Belt, and at the other end the boxes fall off.

In other words, because logic analyzer memory is limited in depth (number of samples), whenever a new sample is acquired the oldest sample currently in memory is thrown away if the memory is full.

In this mode the analyzer is storing all qualified samples in the trace memory. As the memory fills, older data will be overwritten. If you stop the analyzer before the trigger is found, you will see this pre-trigger storage.

The logic analyzer memory system is similar to a circular buffer. When the acquisition is started, the analyzer continuously gathers data samples and stores them in memory. When memory becomes full, it simply wraps around and stores each new sample in the place of the sample that has been in memory the longest.

New data is written over the oldest data until the specified post-store has been stored.

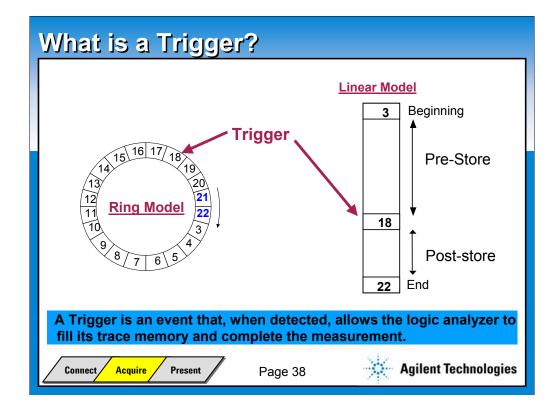

This process will continue until the logic analyzer finds the trigger point. The logic analyzer trigger stops the acquisition at the point you specify and provides a view into the DUT.

The primary responsibility of the trigger is to stop the acquisition, but it can also be used to control the selective storage of data.

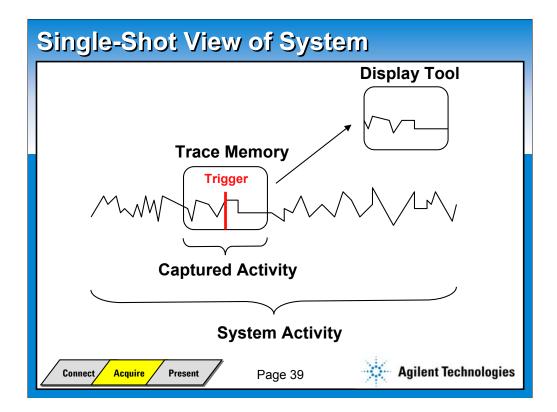

Logic analyzers run in a single shot mode. They continually capture data until a trigger event. They then display the captured data to the screen. The logic analyzer shows one snap shot of the system activity.

| Trigger Positions                |                  |                                                                              |  |

|----------------------------------|------------------|------------------------------------------------------------------------------|--|

|                                  |                  |                                                                              |  |

|                                  | Trigger Position | Use of Trigger                                                               |  |

| Options                          | Start            | Observe code execution                                                       |  |

| Trigger Position - 50% poststore | Center (Default) | View time shortly before/after event                                         |  |

|                                  | End              | Trace cause of system halt<br>Root cause analysis<br>(uncorrelated symptoms) |  |

|                                  | 0-100%           | Variable, custom selection                                                   |  |

|                                  |                  | Aniland Teachard Incide                                                      |  |

| Connect Acquire Present          | Page 40          | Agilent Technologies                                                         |  |

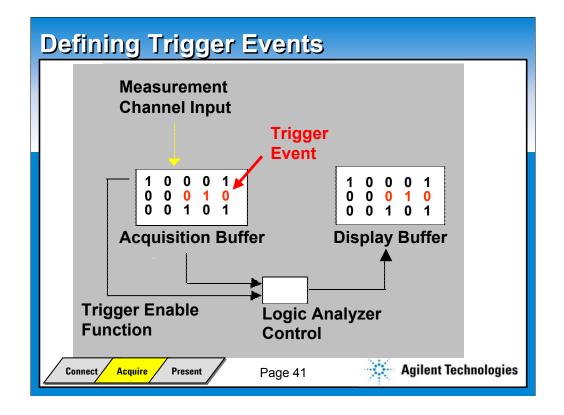

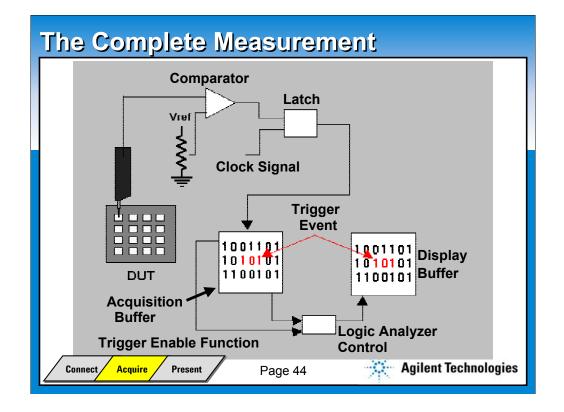

Since digital circuits produce data continuously, the desired data must be isolated. This is accomplished by enabling the logic analyzer to recognize a trigger event—usually a distinctive data pattern.

The analyzer continuously stores data in an acquisition buffer while searching for the trigger event. Once the trigger event is found, [1] the logic analyzer transfers the contents of the acquisition buffer to the display buffer for display and examination.

The analyzer's state specification menu can define a trigger event based on any address, data or control bus state condition. In this example, the logic analyzer stores all measured data until it detects the trigger event, [show 1] which is the address bus state of "043A."

| Trigger Functions Trigger Sequence   Step 1 * Advanced II/Then   \$\$ Edge \$\$ Bus/Signal \$\$ Bus/Signal \$\$ Bus/Signal \$\$ Bus/Signal \$\$ Bus/Signal \$\$ Signalt \$\$ Bising Edge \$\$ find * Bus/Signal \$\$ Signalt \$\$ Bising Edge \$\$ find * Bus/Signal \$\$ Signalt \$\$ Bising Edge \$\$ find * Bus/Signal \$\$ find * Bus/Signal \$\$ find * Bus/Signal <td< th=""><th>Defining Advanced Trigger Events</th></td<> | Defining Advanced Trigger Events                                                                                                                                                                                                                                  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Big Step 1 * Advanced II/Then   Edge Edge   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I   I I |  |

Upon finding the trigger event, the analyzer continues making measurements until the acquisition buffer is full. It displays the results with the trigger event in memory location +0000.

The digitizing functions of comparing and clocking, combined with the control function of trigger enabling, provide all the capabilities needed for making a logic analyzer measurement. To complete the measurement, the contents of the display buffer are transferred to the logic analyzer screen for the user to view and analyze.

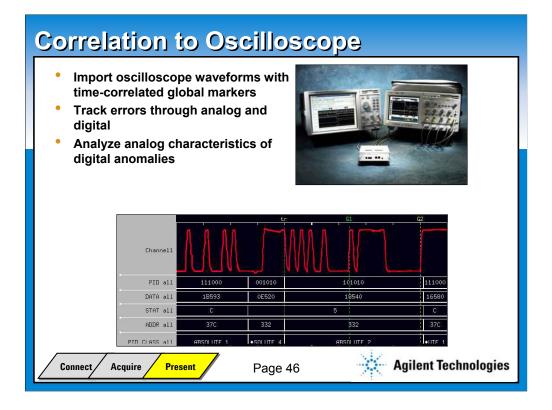

If you require full logic analysis capabilities, but also require higher performance oscilloscope capabilities than are currently available in a standard logic-centric solution, then the Time Correlation Tool may be the best choice for your mixed analog & digital signal measurement applications. This type of solution is basically tying together a full-fledge logic analyzer with a full-fledge oscilloscope with a time-correlation fixture. On the surface you might think that this particular measurement solution has no compromises since each instrument has its own key contribution without compromises. Unfortunately, even this solution has its compromises. But let's take a look at the advantages first...

## Analyzing the Digital-to-Analog Converter Output

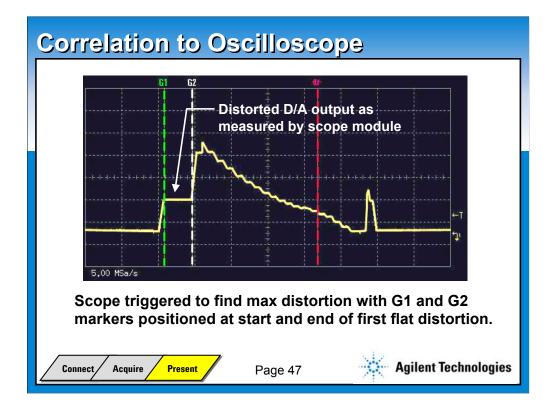

When we take a closer look at the D/A converter's output using the logic analyzer's oscilloscope acquisition module, we occasionally see undesirable "flat-spots" on both the rising and falling edge of the triangular output waveform of the D/A converter. This is what is causing the intermittent "jerky" response of our mechanical output device. So, what is causing this intermittent problem?

The next step would be to set up a trigger condition that reliably catches only the "bad" output conditions. We can do this with a time-qualified trigger condition. We can now clearly see various flat distortions with every acquisition of the scope. We would now like to correlate this output condition with the controlling software. So, we should set up the global markets (G1 & G2) to bracket the longest flat distortion shown on screen.

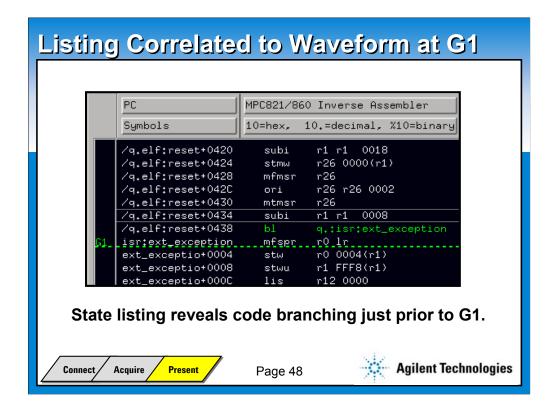

## Listing Correlated to Waveform at G1

However, when we look at the state listing that is time-correlated with the scopes acquisition at the point of the first global marker (G1), we see that at this point the firmware exits execution of the D/A code, and then branches off to somewhere else. So, where does it go?

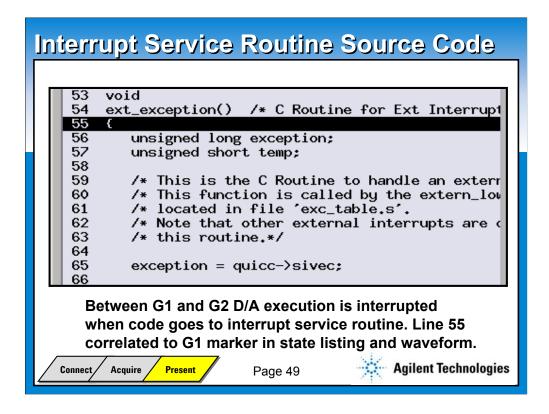

## Interrupt Service Routine Source Code

Looking at the source code again, we can see that during code execution, the code branches off to a priority interrupt routine. So while this interrupt routine is being processed, naturally the output of the D/A converter stays flat at a constant DC level. Once the interrupt routine has finished processing (G2 marker), the D/A code continues to generate the desired analog ramping voltage.

Problem discovered! For smooth actuation of our embedded output device, the D/A converter needs to take priority over any interrupts. For the software/firmware designer, this should be an easy fix.

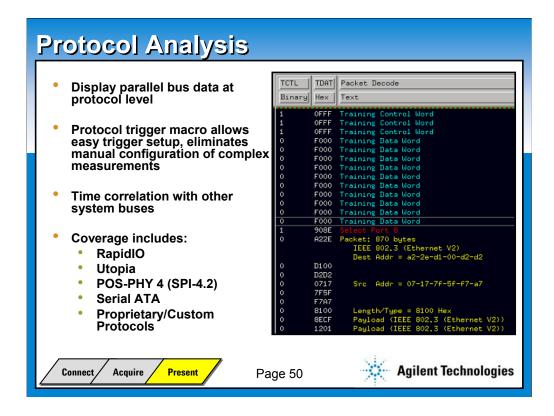

Another addition to the logic analyzer's data views are the packet decoders for various protocol analysis needs. This moves beyond the traditional state Listing display and provides with the level of packet detail needed to gain insight from the data

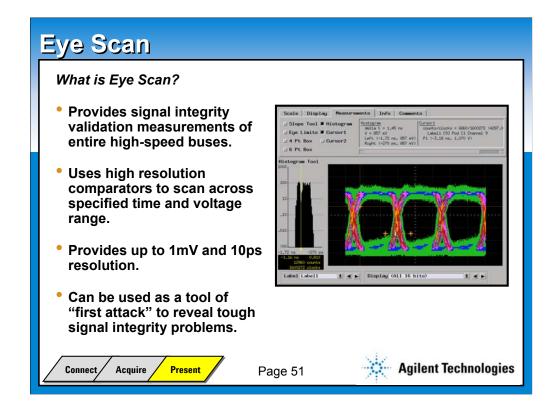

With Eye Scan in the logic analyzer, you can get a composite eye-diagram display of ALL signals on a bus for validation purposes. With a scope, you are limited to the number of channels of the oscilloscope.

The actual acquisition technique is very different from real-time oscilloscopes, but since eye-diagrams are fundamentally a repetitive measurement, the results are similar. With Eye Scan, high resolution comparators scan across a time and voltage range specified by the user with up to 1mV and 10ps resolution. This type of tool is ideal as a "first attack" approach for revealing tough signal integrity problems across an entire bus.

Eye scan is a great compliment to an oscilloscope. The logic analyzer will allow you to look at al of the channels simultaneously and identify where the problem signals are. From there, the scope can be used to determine the parametric characteristics of the bgtroublesome signal.

| Using a Logic Analyzer vs. an Oscilloscope           |                                                                                    |                                                   |  |  |

|------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------|--|--|

|                                                      | Use a Logic Analyzer to:                                                           | Use an Oscilloscope:                              |  |  |

|                                                      | See many signals at once                                                           | To get precise time interval information          |  |  |

|                                                      | Look at signals the same way your hardware does (State                             |                                                   |  |  |

|                                                      | Mode)                                                                              |                                                   |  |  |

|                                                      | Trigger on a pattern of highs<br>and lows on several lines and<br>see the result   | To look at the analog characteristics of a signal |  |  |

|                                                      | Verify timing relationships<br>among several or hundreds<br>of lines (Timing Mode) |                                                   |  |  |

| Connect Acquire Present Page 53 Agilent Technologies |                                                                                    |                                                   |  |  |

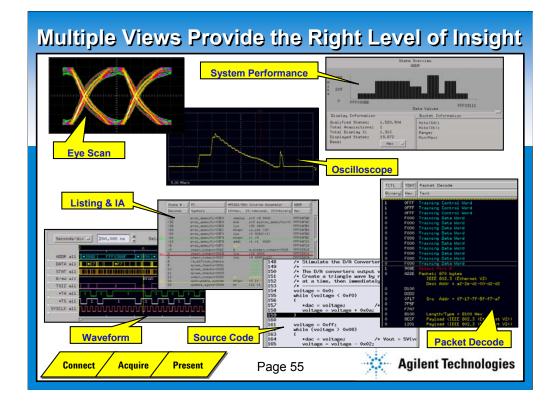

Agilent has always provided a variety of ways to view your data for analysis purposes. The traditional waveform and listing views, as well as the correlation to source code and oscilloscope views are still there. The Eye Scan and Packet Decode views we just discussed are simply new additions to the robust tools already available that extend your ability to analyze the data and gain quick insight.

In a moment we will begin with the Q&A but 1<sup>st,</sup> for those of you who have enjoyed today's broadcast, Agilent Technologies is offering a new service that allows you to receive customized Email Updates. Each month you'll receive information on:

•Upcoming events such as eSeminars, seminars and tradeshows

•the latest technologies and testing methods

new products and services

•tips for using your Agilent products

•updated support information (including drivers and patches) for your Agilent products

It's easy to subscribe and you can change your preferences or unsubscribe at anytime. Once you've completed the NetSeminar feedback form you will be directed to Agilent's resource page located on slide # XX, at that point simply click on the Agilent Email Updates link and you will be directed to the subscription site.

Now on to the feedback form then to Q&A......